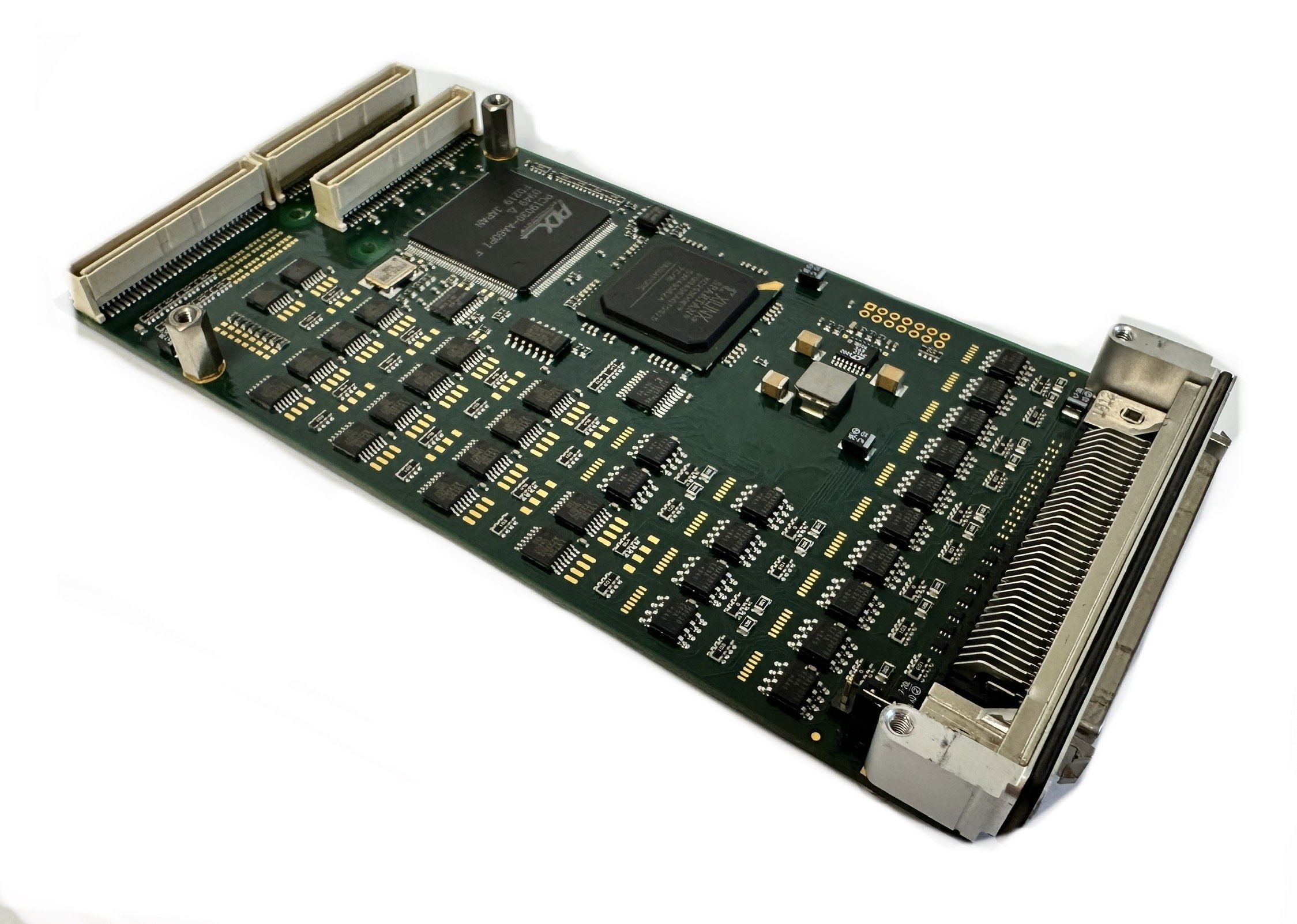

Product Specifications

Standard single-width 32 bit PMC module conforming to IEEE P1386.1

PCI 2.1 compliant interface

3.3V and 5V PCI Signaling Voltage

Board size: 149 mm x 74 mm

TPMC630-1x: Xilinx XC2S300E-6 Spartan-IIE FPGA configured by serial Flash XCF02S TPMC630-2x: Xilinx XC2S600E-6 Spartan-IIE FPGA configured by serial Flash XCF04S

Flash device in-system programmable

32 bit PCI target interface by PLX PCI9030

FPGA clock options:

Local clock oscillator

PLL programmable clock generator (200 KHz – 166 MHz), 6 clock outputs connected to FPGAI/O lines

64 TTL I/O (-10), 32 differential I/O (-11) or 32 TTL I/O and 16 differential I/O (-12)

TTL signaling voltage (maximum current: +/-32mA) or EIA-422/-485 signaling level

direction individually programmableI/O access:

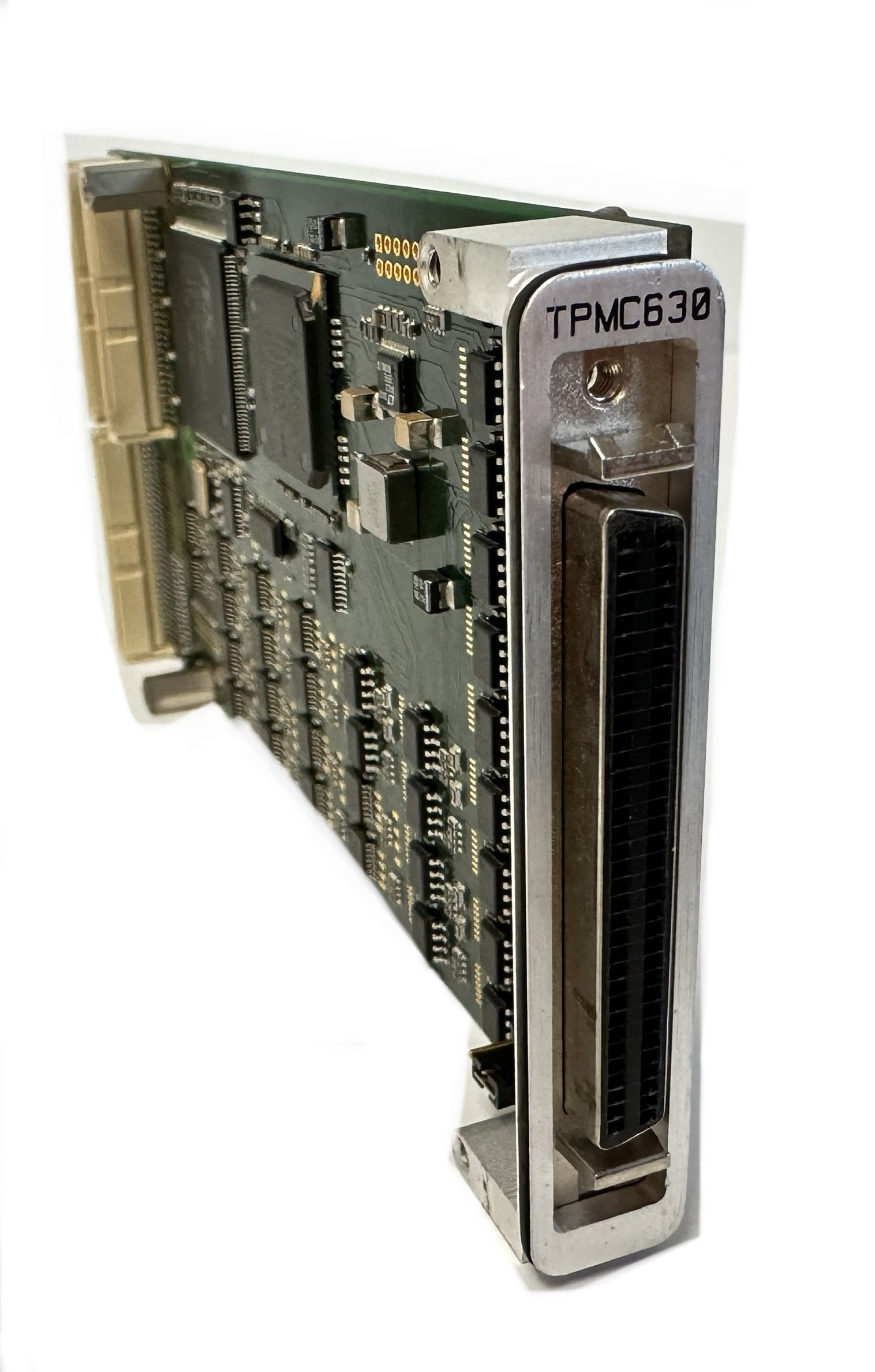

64 I/O lines on HD68 front connector, parallel to up to 64 I/O lines on rear connector P14

Operating temperature: -40°C to +85°C

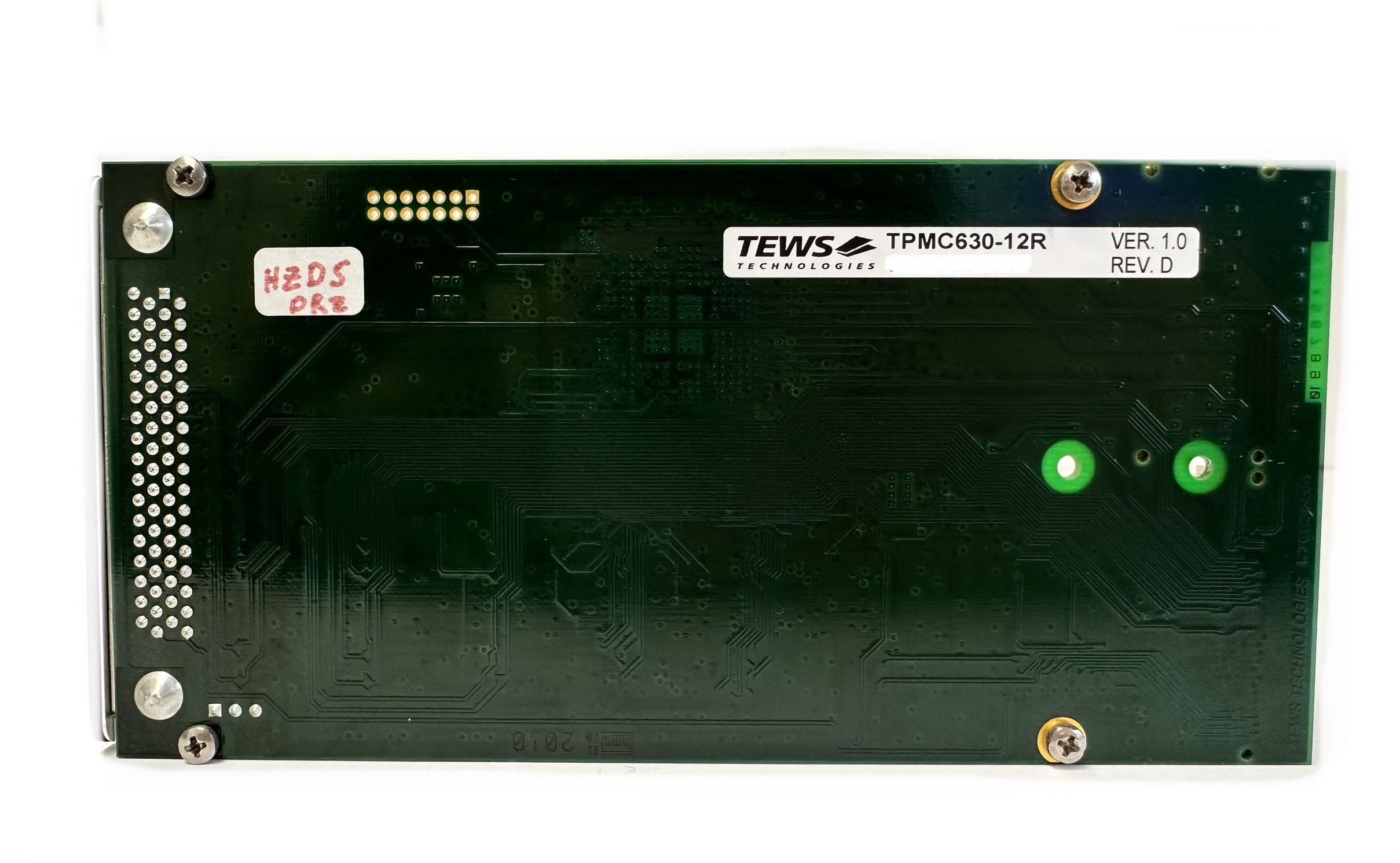

Manufacturer by TEWS Technology. Product is refurbished in good condition.

The TPMC630 is a standard single-width 32 bit PMC module providing a user configurable FPGA with 300,000 (TPMC630-1x) or 600,000 (TPMC630-2x) system gates. All local signals from the PCI controller are routed to the FPGA. The TPMC630-x0x has 64 ESD-protected TTL lines, the TPMC630-x1x provides 32 differential I/O lines using EIA-422 / EIA-485 compatible, ESD-protected line transceivers. The TPMC630-x2x provides 32 TTL and 16 differential I/Os. All lines are individually programmable as input or output. The receivers are always enabled, which allows determining the state of each I/O line at any time. This can be used as read back function for lines configured as outputs. Each TTL I/O line has a pull-up resistor. The pull-up voltage is selectable to be either +3.3V or +5V. The differential I/O lines are terminated by 120Ω resistors.

SKUE5

Qty 1

Alternative P/N: TPMC630 12R