Price: Contact Us

Email: sales@esi-technologies.com

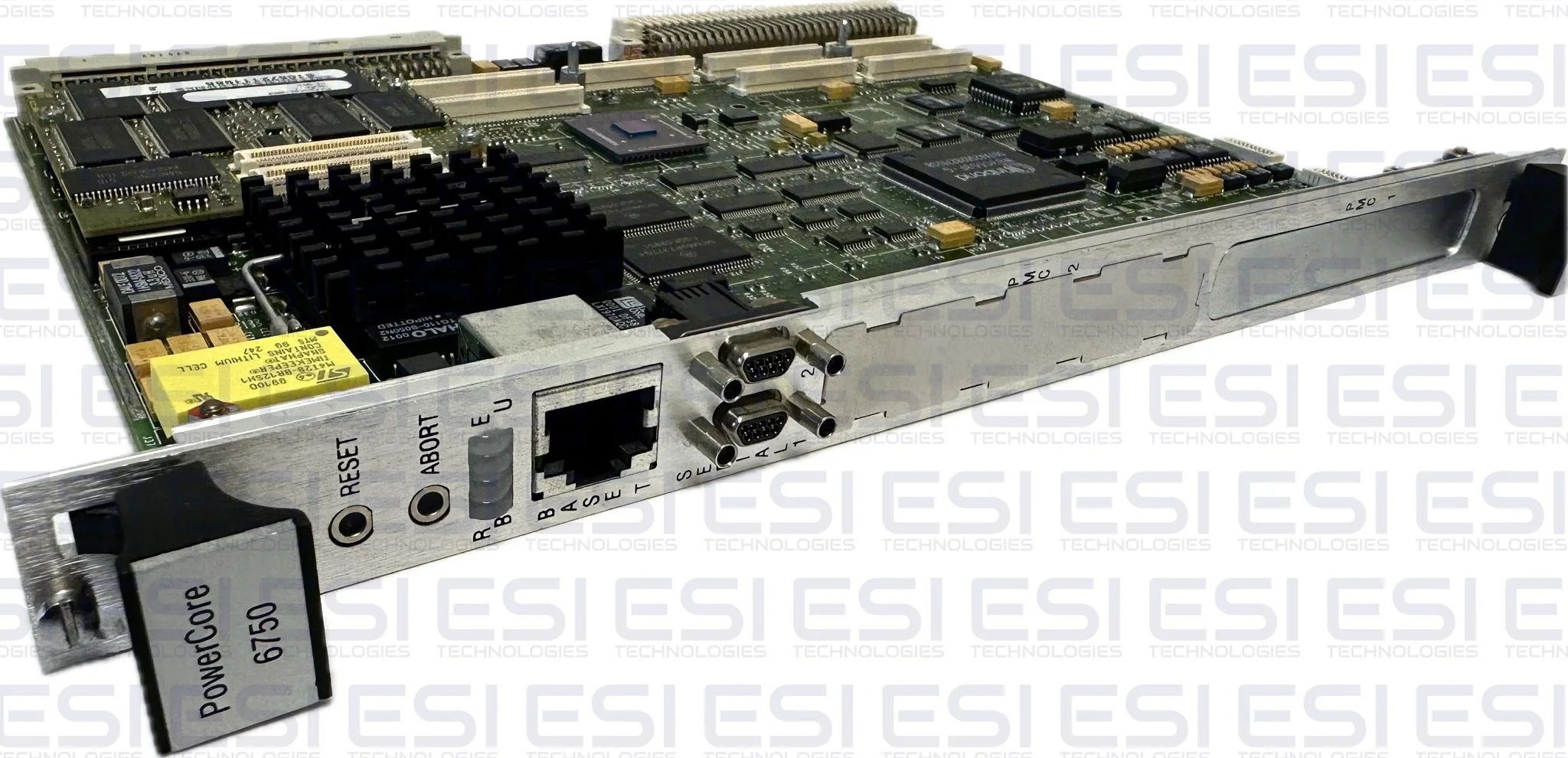

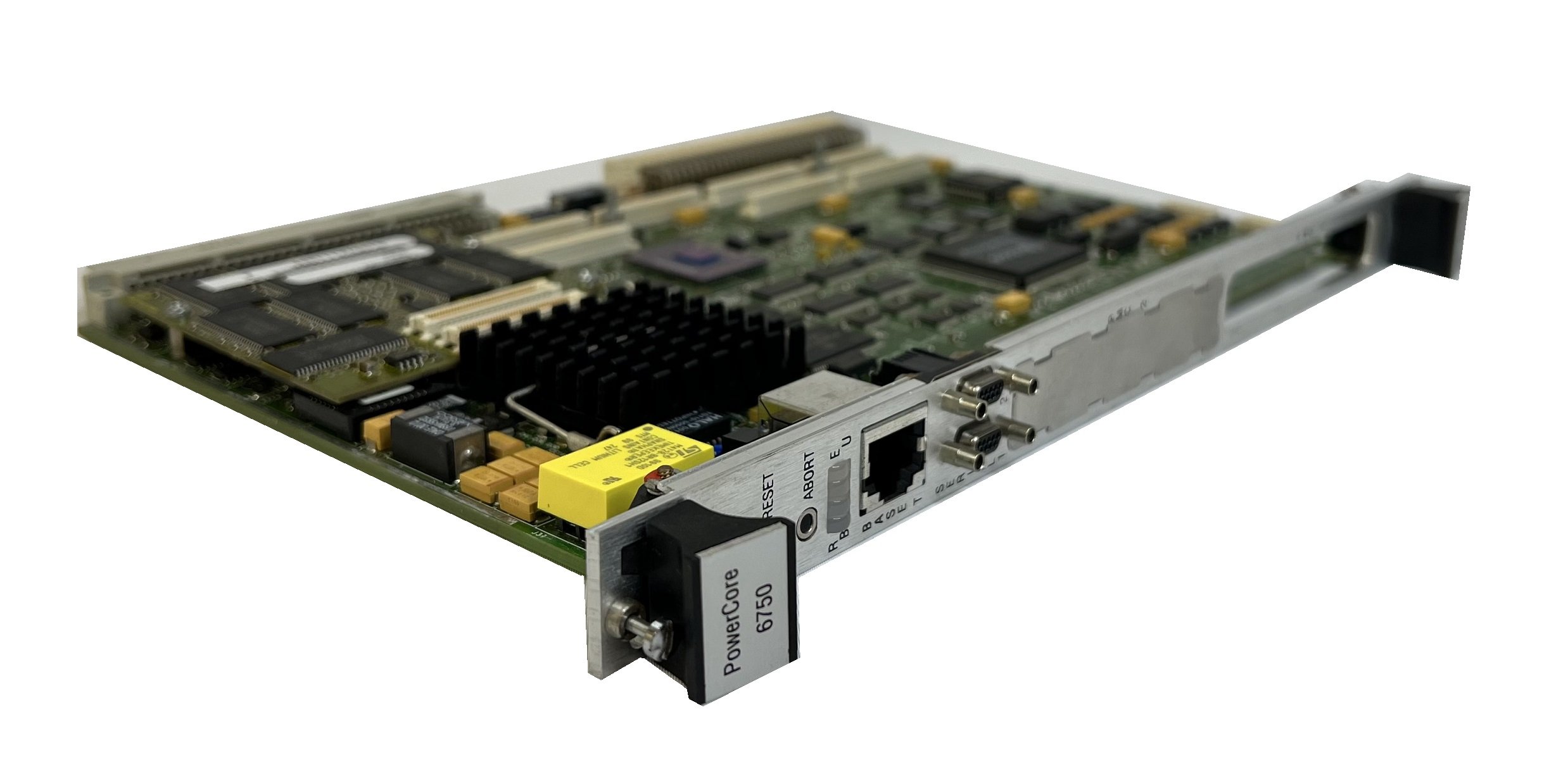

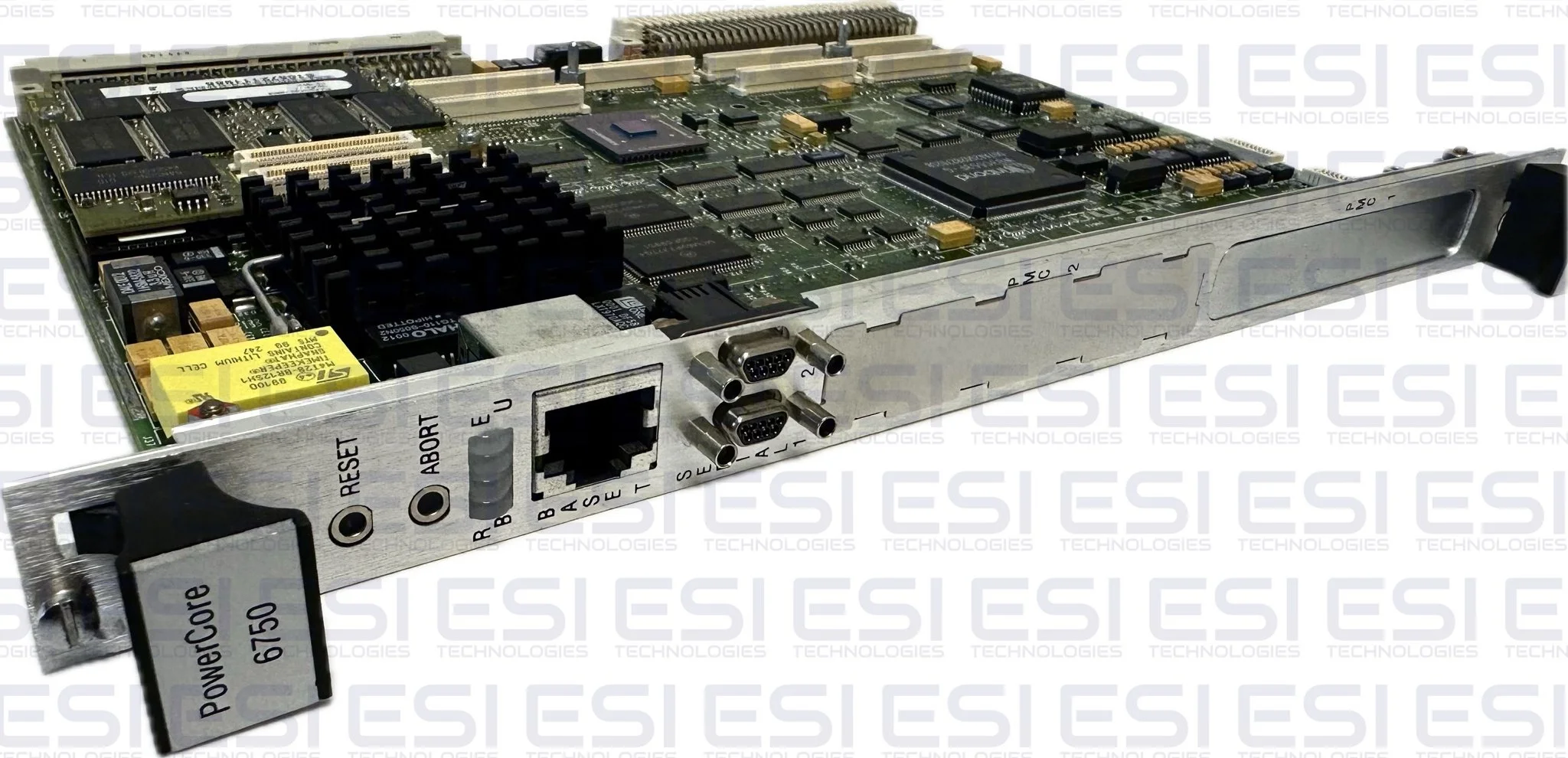

Condition: USED

Location: SKUE3

In Stock: 3

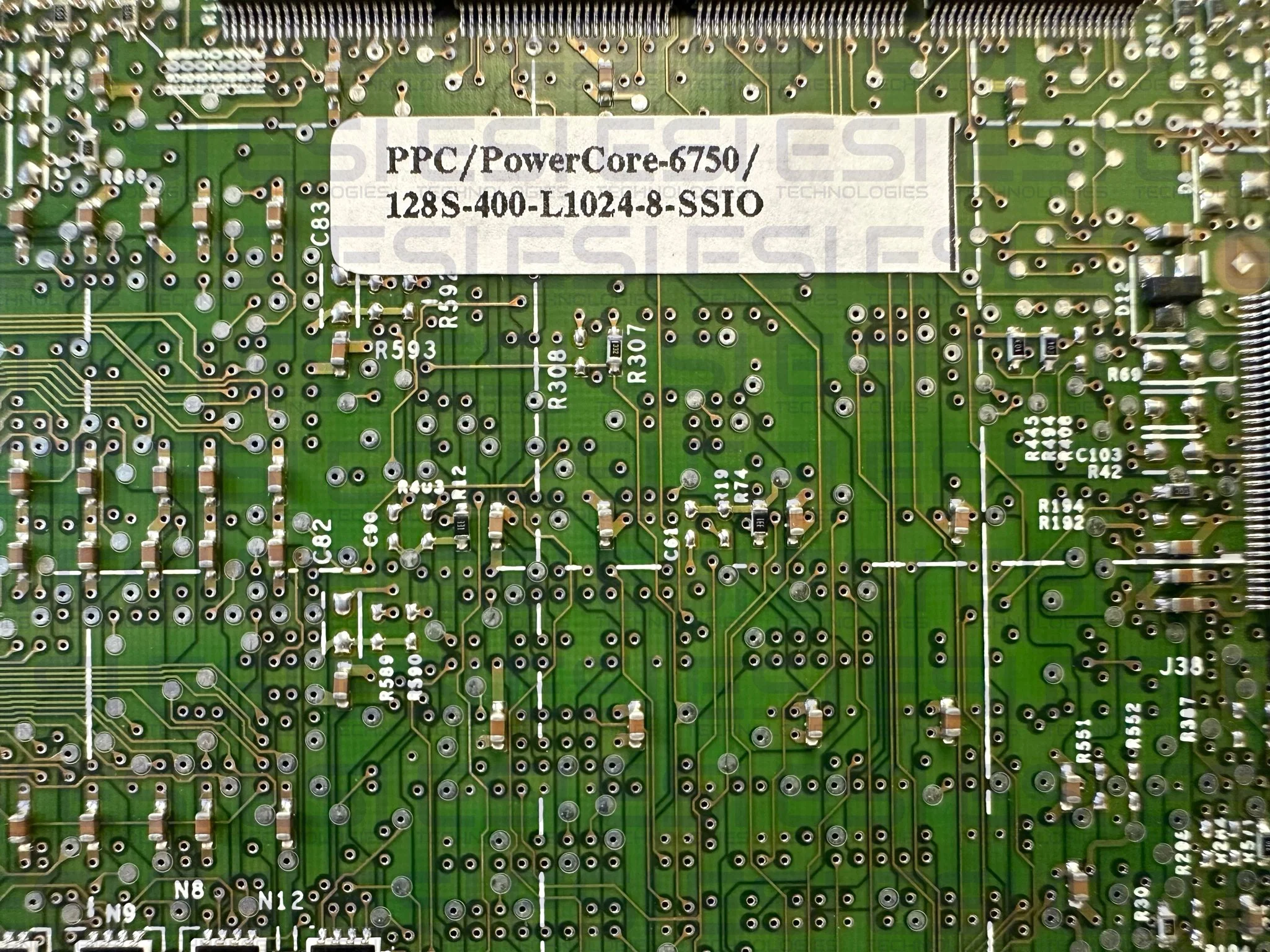

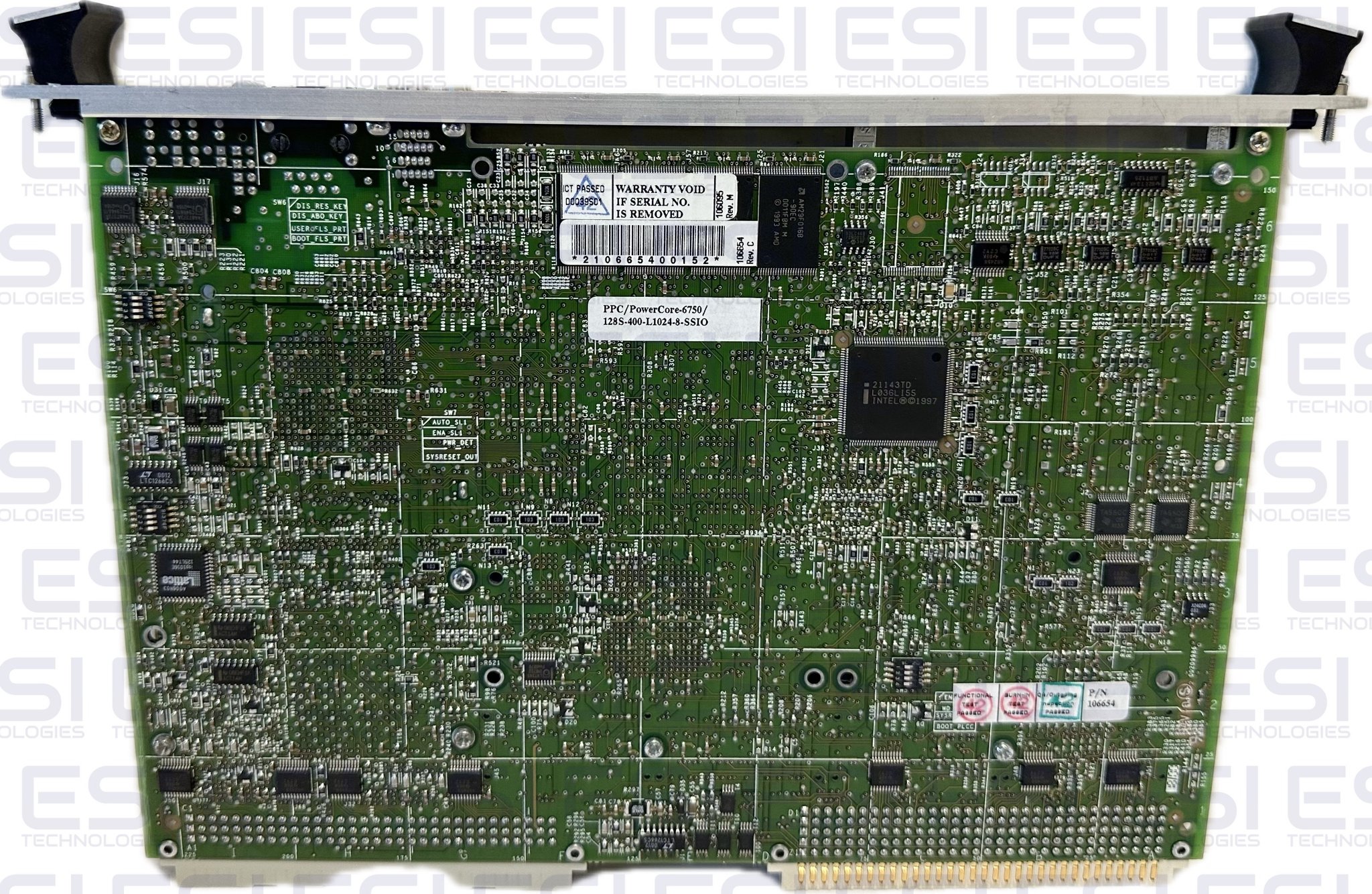

Product Specifications

The shared memory is accessible from:

PowerPC CPU, Universe II DMA controller

Other VMEbus masters, Ethernet DMA controller

Other PCI DMA controllers on PMC modules

PCI-to-ISA bridge DMA controller.The capacity of the shared memory is encoded in the DCCR.

The EDO DRAM is arranged in one or three memory banks with nine 2M * 8 or 8M * 8 EDO DRAM devices in each bank.

The SDRAM is arranged in one, three, or four banks with eight 8M * 8 SDRAM devices in each bank. Each memory module bank is 64-bit wide. The EDO DRAM memory

banks provide one additional byte for the ECC.

The PCI interface implements the following features:

Compliant with PCI 2.1

Operation at 33 MHz

PCI interlocked accesses to shared memory via lock pin and lock protocol

Accesses to all PCI address spaces

Selectable big or little endian operation

Store gathering of PPC-to-PCI writes and PCI-to-memory writes and memory prefetching of PCI read accesses

PCI configuration registers

Data buffering (in/out)

Parity support

The microprocessor PowerPC 750 manufactured by Force Computers is one of the basic components of the PPC/PowerCore-6750. The PowerPC 750 consists of a processor core and an internal L2 tag combined with a dedicated L2 cache interface and a PPC bus. It provides, 32-nit effective addresses, integer data types of 8,16, and 32 bits, floating-point data types of 32 and 64 bits. PPC/PowerCore-6750 provides an L2 cache of up to 1 MByte. The L2 cache is controlled by the L2 cache controller of the PowerPC 750. The L2 tag is 2 way set associative with 4-K entry tags per way. Only the memory space of the processor bus devices can be cached in the L2 cache.

Alternative Part No. PPC, PowerCore-6750, PowerCore6750, 106721